# Using Interactive Hybrid Online Labs for Rapid Prototyping of Digital Systems

http://dx.doi.org/10.3991/ijoe.v10i5.3994

K. Henke<sup>1</sup>, G. Tabunshchyk<sup>2</sup>, H.-D. Wuttke<sup>1</sup>, T. Vietzke<sup>1</sup>, St. Ostendorff<sup>1</sup> <sup>1</sup> Ilmenau University of Technology, Ilmenau, Germany <sup>2</sup> Zaporizhzhya National Technical University, Zaporizhzhya, Ukraine

Abstract—The Ilmenau Interactive Hybrid Online Lab has offers several fields of application. In this article an enhancement of the existing Online Lab will be described to al provide additional functionalities for a Web-based rapid prototyping of digital systems as well as the Web-based verification of such systems. For this new operation mode of the online lab a special rapid-prototyping board for digital systems was developed to fulfill the design tasks of digital systems. All the components of the rapid prototyping board will be described in detail. The implemented online lab infrastructure allows to interconnect online labs and to protect the system of the protect of the system of the

*Index Terms*—control engineering education, laboratories, Web-based education, virtual and remote labs, Web-based design tools, distance learning, rapid prototyping.

ties worldwide.

# I. INTRODUCTION

In our contribution we would like to present an enhancement of the Ilmenau Interactive Hybrid<sup>1</sup> Online Lab to provide additional functionalities for a Web-based rapid prototyping of digital systems as well as the Web-based verification of such systems. Facilities of Hybrid Online Labs provide permanent online access for students and supervisors, and give possibilities to check different parts of the designs most easily. This gives possibilities to realize correct designs, to organize self-study process of the student more efficiently, to control student's work and to broaden the ways of communication in research work with companies. This solution is intended

- for the use in teaching materials dealing with the design of digital control systems and embedded systems – from the basics up to complex design tasks as well as

- within the newly established Tempus project "ICo-op – Industrial Cooperation and Creative Engineering Education based on Remote Engineering and Virtual Instrumentation", founded by the European Commission of the program "Tempus", Grant No 530278-TEMPUS-1-2012-1-DE-TEMPUS-JPHES [1].

The main topic of this Tempus project is to empower university-enterprise partnerships in Armenia, Georgia, and Ukraine by modernizing engineering education based on remote engineering and virtual instrumentation enhanced with transversal knowledge and competences at universities. It also offers new possibilities for bidirectional cooperation between universities and enterprises in education and research. The remote teaching of enterprise's staff or usage of universities remote labs for research purposes is one example for such cooperation. In order to achieve this, Ilmenau Interactive Hybrid Online Labs will be put in place at several project partners to develop common learning modules and to interchange these modules between all the partners - based on EU best practices, partners' industry expertise, and knowledge of business demand of target countries.

Within the Tempus project a bilateral agreement be-tween Ilmenau University of Technology and Zaporizhzhya National Technical University (ZNTU) was signed as well. The main purpose of this cooperation is to engage in joint scientific work in the fields of Automation Systems, Computer and Software Engineering and Remote Engineering, using the Ilmenau Interactive Hybrid Online Lab for this purpose. The Institute of Computer Science and Radio Electronics of ZNTU is in close contact with the leading specialized enterprises of the Ukrainian region. But unfortunately it is tended to reduce the number of diplomas ordered by enterprises during last years. One of the factors is difficulties in communication between student, university supervisor and company supervisor. Further is considering how Hybrid Online Lab can solve this problem as well providing an effective remote tool for different level designs.

# II. RAPID PROTOTYPING OF DIGITAL SYSTEMS

With the described enhancement of the functionality we want to provide exciting and challenging Web-based lab experiments in the field of digital system design. Course material starts with the basics of Boolean algebra, combinational logic and simple sequential circuits. This is followed by various minimization techniques for logical expressions, dynamic effects in combinational and sequential circuits and the design of digital control systems based on Finite State Machines (FSM). Finally we offer different methods and tool concepts to create, implement and validate digital systems to solve complex design tasks.

The goal is to introduce methods and technologies for a rapid prototyping of digital (embedded) control systems, especially the hardware oriented part of these systems. In connection with the mentioned Tempus project design engineers working in industry may also want to consider the offered learning scenarios of the project to handle modern CAE tools, logic simulation and logic synthesis using hardware description languages (e.g. VHDL), de-

<sup>&</sup>lt;sup>1</sup> Hybrid online labs provide both remote experiments on real electromechanical models (physical systems) in the remote lab as well as simulation models of these physical systems in virtual labs [2].

sign hierarchy, and current generation of field programmable gate array (FPGA) technology – if they have not had previous experience with these rapidly evolving technologies. With modern logic synthesis tools and large FPGAs, more advanced designs are needed to present challenging laboratory projects.

# III. ARCHITECTURE

The concept and the architecture as well as different fields of application of the Ilmenau Interactive Hybrid Online Lab were presented in various publications during the last years in detail, e.g. in [3, 4, 5]. A special rapid prototyping board for digital systems was developed for the new operation mode of the Ilmenau Interactive Hybrid Online Lab, presented in this paper to fulfill the mentioned design tasks. All the components of the rapid prototyping board will be described in detail in the following sections.

# A. The Ilmenau Interactive Hybrid Online Lab

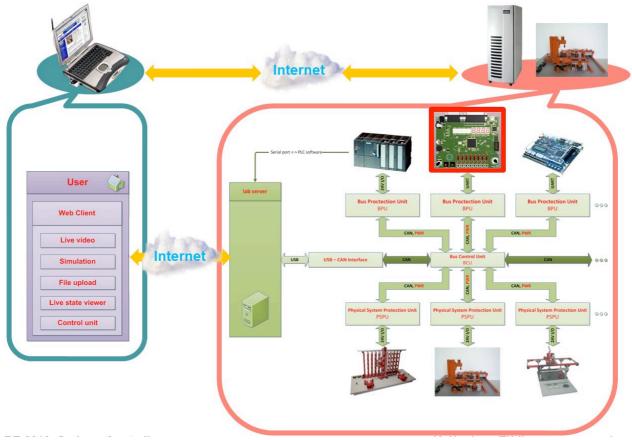

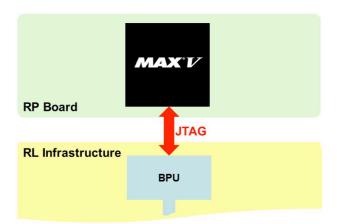

Figure 1 gives an overview about the Ilmenau Interactive Hybrid Online Lab. The infrastructure is based on a universal grid concept which guaranties a reliable, flexible as well as robust usage of this online lab. A more detailed description of this grid concept as well as the main components is presented in [5, 6].

The server side infrastructure (remote lab) consists of three parts:

- an internal serial *remote lab bus* to interconnect all parts of the remote lab, realized as CAN bus,

- a *bus protection unit* (BPU) to interface the control units to the remote lab bus and to protect the bus from blockage, misuse and damage as well as

• a *physical system protection unit* (PSPU), which protects the physical systems (the electro-mechanical models in the remote lab) against deliberate damage or accidentally wrong control commands and which offers different access and control mechanisms.

The interconnection between the Web-control units and the selected physical systems during a remote lab work session (experiment) as well as the webcam handling is done by the lab server as part of the remote lab infrastructure.

During a running experiment, the client application will interact directly with the online lab grid infrastructure. Based on this infrastructure we offer several operation modes, described in detail in [3, 5]. In the following we would like to present an enhancement of the existing operation modes to provide additional functionalities for a Web-based rapid prototyping of digital systems as well as the Web-based verification of such systems.

# B. The Rapid Prototyping Board

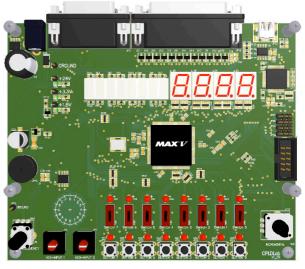

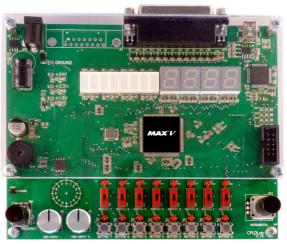

To fulfil all the mentioned design tasks for the design of digital systems, we have developed a special rapid prototyping board, shown in Figures 2 and 8. Over the last years, a number of interesting and challenging rapid prototyping boards were developed for educational purposes, e.g. the UP 3 from Altera [7] or development boards from Xilinx [8]. But most of them support very specific design tasks – not the whole spectrum, needed from the beginning (e.g. students in the first semester) to exciting and challenging design tasks in high-level courses.

Figure 1. Overview of the Ilmenau Interactive Hybrid Online Lab infrastructure

## **REGULAR PAPER**

## USING INTERACTIVE HYBRID ONLINE LABS FOR RAPID PROTOTYPING OF DIGITAL SYSTEMS

Our rapid prototyping board is based on the MAX<sup>®</sup> V -5M1270Z CPLD from Altera [9]. With its mix of low price, low power, and new features, the MAX V CPLD family delivers the market's best value. Featuring a unique, non-volatile architecture and one of the industry's largest density CPLDs, MAX V devices provide robust new features at up to 50 percent lower total power compared to competitive CPLDs. The MAX V architecture integrates previously external functions, such as flash, RAM, oscillators, and phase-locked loops [9].

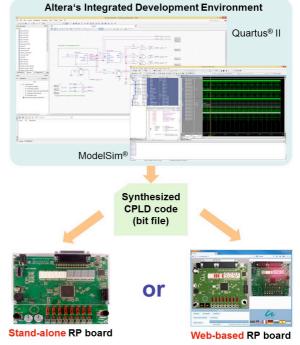

MAX V CPLDs are supported by the free Quartus<sup>®</sup> II Web Edition development software. With Quartus II software, students will get productivity enhancements resulting in faster simulation, faster board bring-up, and faster timing closure [10].

Finally, students can use the free Quartus II simulator tool QSim (with an integrated waveform editor). QSim is a graphical user interface (GUI) that is used to run simulations and launch the Waveform Editor. Also, QSim is used to set whether the simulation should be a functional or timing simulation. The Vector Waveform Editor is used to draw the test input signals for the simulation and select which signal should be shown in the simulation results [11]. In High-level courses students can use the more powerful simulation tool Model*Sim*<sup>®</sup> to validate the design. Model*Sim* supports behavioral and gate-level simulations, including VHDL testbenches [12].

Besides the MAX V CPLD the rapid prototyping board consists of the following components (see Figure 2):

- Input buttons:

- o 8 pushbuttons:

- PB\_7 .. PB\_4 (active low)

- PB 3.. PB 0 (active high)

- o 2 rotary hexadecimal encoder

- 8 slide switches

- LED outputs:

- 47-segment displays (active low)

- 1 LED bar display with 8 LED (active low)

- Other components:

- o 10.000 MHz crystal oscillator

- Frequency synthesizer (200 Hz .. 10 kHz)

- Piezoelectric oscillator (for "sounds")

- o Incremental encoder

- o UART (over USB)

- 25-pin SUB-D connector (to connect additional hardware boards, e.g. for a VGA adapter)

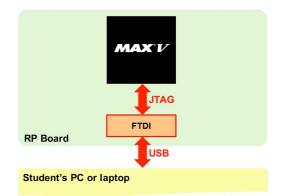

To program the MAX V CPLD on this stand-alone version of the rapid prototyping board, an additional FTDI chip [13] was placed on the board. The student has to connect the prototyping board via USB to his PC or laptop to upload the synthesized CPLD design to the FTDI chip at the prototyping board. This chip will program the CPLD automatically via JTAG interface (see Figure 3).

## C. The Online Lab Rapid Prototyping Mode

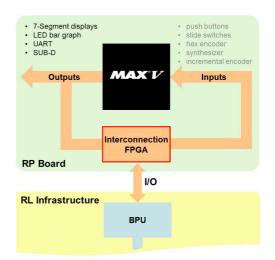

For a Web-based usage of the rapid prototyping board, an additional "interconnection" FPGA is placed on the bottom side of the PCB to realize the communication with the remote lab infrastructure (see Figure 4). All inputs of the board (buttons, synthesizer, incremental encoder and oscillator) have to be removed from the PCB and are replaced by a direct connection to the outputs of the "interconnection" FPGA, which will set all input signals according to the user's input via the user interface at the student's client PC. The generated outputs of the prototyping board can be directly read by the "interconnection" FPGA without removing any LED. The FPGA is interconnected to the BPU within the remote lab infrastructure.

Figure 2. Rapid prototyping board (schematic view)

Figure 3. Programming of the stand-alone rapid prototyping board

Figure 4. Interfacing the rapid prototyping board to the remote lab

# REGULAR PAPER USING INTERACTIVE HYBRID ONLINE LABS FOR RAPID PROTOTYPING OF DIGITAL SYSTEMS

To program the MAX V CPLD on the prototyping board in the remote lab via the Internet, the existing remote lab infrastructure can be used, as shown in Figure 5. The student has to upload his synthesized design (FPGA programming file) via the RIA (Rich Internet Application – a consistent enhancement of previous Java applets – see next section) on his client PC at home to the remote lab. Then the remote lab server will forward the data to the corresponding BPU (compare Figure 1). The BPU in turn will program the connected CPLD automatically via JTAG.

# D. The Web-based User Interface

The increasing capacity of wireless communication and the growing number of mobile devices (e.g. smartphones and tablets) on the one hand as well as modern Internet technologies like JavaScript, HTML5 and Web Sockets on the other hand provides new possibilities and challenges in the area of mobile learning. Therefore a realization as HTML5 RIA was chosen for the Web-interface. Figure 6 gives an impression of this Web-interface.

By using the client's Web-interface, the student is able to upload the synthesized CPLD code of the design to program the CPLD on the rapid prototyping board (automatically in the remote lab – see section III.C) and to handle the whole lab procedure. This Web-interface allows the student to manipulate all the inputs of the rapid prototyping board virtually (slide switches, hex coding switches, pushbuttons and incremental encoder).

For the look-and-feel of the RIA, we use a visual model of the prototyping board (on the upper left side). All the inputs are realized as HTML5 control elements and can be activated via a mouse interactively. Changes are immediately sent to the rapid prototyping board in the remote lab and the corresponding results are displayed again inside the visual model. Furthermore a webcam will be used to observe the rapid prototyping board (on the upper right side) to watch the results of the user's actions directly as reaction in the remote lab.

# IV. FIELDS OF APPLICATION

In this section possible fields of application of the developed rapid prototyping platform will be discussed.

Following the design flow for digital systems, students have to use common design tools to implement their control tasks. As mentioned in Section III.B they have to use Altera's development system (Quartus II, simulation tools).

After synthesizing the bit file as shown in Figure 7, students can use the prototyping board as

- stand-alone system (see Section IV.A) or

- Web-based rapid prototyping system (see Section IV.B and IV.C).

# A. Stand-alone Rapid Prototyping System

The simplest way to use the designed hardware platform is as a stand-alone solution for the rapid prototyping of digital systems (without Internet connectivity), shown in Figure 8. This application is not the focus of this article and therefore not discussed in detail.

Figure 5. Web-based programming of the rapid prototyping board via the remote lab

Figure 6. Web-interface of the rapid prototyping board (RIA)

Figure 7. Using Altera's IDE and the rapid prototyping board for the design of digital control tasks

# **REGULAR PAPER**

## USING INTERACTIVE HYBRID ONLINE LABS FOR RAPID PROTOTYPING OF DIGITAL SYSTEMS

# B. Web-based Prototyping of Digital systems

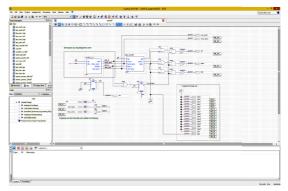

By using the mentioned Altera's development system, students are able to specify their design via:

• *Text based* design methods,

Here the student can enter his design by means of logical equations, truth tables or hardware description languages (AHDL, VHDL or Verilog), as shown in Figure 9.

• *Graphically* based design methods,

The student can use block or schematic diagrams to input his design, as shown in Figure 10.

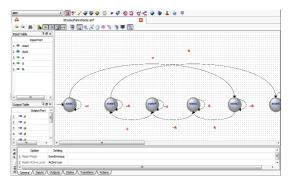

• Integrated *FSM editors*.

In case of sequential design tasks he can directly enter the derived automaton graph (or graphs of parallel automata) with the built-in FSM editor, as shown in Figure 11.

The editor itself generates VHDL code for the further design steps.

Furthermore, students can specify, describe, implement and verify different digital systems using "self-made" IP core libraries (e.g. digital control systems, serial communication modules, robot sensors control, models of RISC processors, etc.).

After specification of the given task, students have to simulate their design. They can choose between different simulation tools within Altera's development system, e.g. Model*Sim* for challenging designs in high-level courses.

Once the design is completed and error free, the student can upload the synthesized design to the remote lab, program the CPLD on the prototyping board (as described in Section III.C) and can test his solution using the rapid prototyping platform.

## C. Web-based Validation of Digital Systems

Another use case of the rapid prototyping board is

- to identify the function of a given design (black box) or

- to find malfunctions of a given well-known design.

The CPLD will be pre-programmed by the teacher and the student has no ability to reprogram the device.

By manipulating the inputs of the unknown black box (e.g. to enter all the input sets of a truth table or special input sequences), the student attempts to analyze the response (the real output signals) of the board to find out the function of the given design. The student has to enter his test vectors based on truth tables or input sequences one by one using the provided controls and observe the results.

It is planned to support the upload of a whole truth table or input sequence as a text file via the Web-interface of the prototyping board. In this case the student will be able to record the responses corresponding to the specified inputs creating a waveform file. This file can then be used for further investigation of the current design.

Figure 8. Rapid prototyping board

| le Edit | Wew Project Processing Tools Window Help 🕫 Search altera /                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .on    | 0    |

|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|------|

| a #     | 4. (*) 年年 6. 6* 16 4. (*) 1 2 (2) 第2) 二 2 2 2 3 2 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 2 3 4 1 二 2 2 2 3 4 1 二 2 2 2 3 4 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |        |      |

| 76      | ymrr <= '0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |        | -    |

| 77      | cl <= '0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |      |

| 78      | or <= '0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |      |

| 79      | fk c= '0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |      |

| 80      | steu0 <= '0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |      |

| 81      | steul <= '0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |      |

| 82      | steu2 <= '0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |      |

|         | CASE fstate IS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |        |      |

| 84      | WHEN ZO =>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |      |

| 85      | <pre>IF (((((xkr = '1') AND NOT((dr = '1'))) AND NOT((dl = '1'))) OR (((xkl = '1') AND NOT((dr = ')</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1999   | AN   |

|         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |      |

| 87      | ELSIF (((dr = '1') AND NOT((dl = '1')))) THEN<br>reg_fstate <= Z6;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |        |      |

| 88      | reg_fstate <= Z6;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |      |

| 89      | ELSIF ((NOT((dr = '1')) AND (dl = '1'))) THEN reg fstate <= 27;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |      |

| 90      | reg fatate <= 27;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |      |

|         | ELSIF ((((NOT((xkr - '1')) AND NOT((xkl - '1'))) AND NOT((dr - '1'))) AND NOT((dl - '1'))) OF                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | k [[d] | -    |

| 92      | reg_fstate <= Z0;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |      |

| 93      | Inserting 'else' block to prevent latch inference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |      |

| 94      | ELSE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |        |      |

| 95      | reg_fstate <= Z0;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |        |      |

| 96      | END IF;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |        |      |

| 97      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |      |

| 98      | yal <= xlr;                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |        |      |

| 99      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |      |

| 100     | steu2 <= '0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |        |      |

| 101     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |      |

| 102     | cl c= '0';                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |      |

| 103     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |        |      |

| 104     | ar <= 101:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |        |      |

|         | n                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | _      | •    |

|         | 0%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 00:00  | 2:00 |

Figure 9. VHDL text-based specification

Figure 10. Block diagram-based specification

Figure 11. FSM-based specification

### **REGULAR PAPER**

#### USING INTERACTIVE HYBRID ONLINE LABS FOR RAPID PROTOTYPING OF DIGITAL SYSTEMS

## V. CONCLUSION

A universal hardware platform has been discussed, which can be used for rapid prototyping of digital systems. It is used for teaching purposes, from the basics to complex control design tasks including the ability for both local and web-based remote access.

Within several new European projects in the area of "Remote Engineering" e.g. ICo-op [1], eScience [14] and DesIRE [15] it is increasingly necessary to allow and organize a shared use of equipment. Therefor the main focus is a Web-wide usage of design tools and remote labs for the design of digital systems.

Using both, online tool support and laboratories, has the potential of removing the obstacles of cost, time-inefficient use of facilities, inadequate technical support and limited access to design and laboratory resources. This would also benefit students and researchers with special needs and students/researchers working from home, so they do not have to travel to their companies' facilities to perform their work. Even students/researchers working at their university's facilities can use remote specialized equipment at another university without traveling.

Students will learn more about the possibilities and limits of remote control and observation via Internet on practical examples.

The student – besides knowledge consolidation by executing design and practical experiments using these new Internet technologies – is forced to estimate the technologies critically.

#### ACKNOWLEDGMENT

The authors would like to acknowledge the work of Alexander Härtel and Tobias Fäth in the development of the Web-based programmer as well as the Web-based user interface (RIA).

#### REFERENCES

- [1] ICo-op project Website: http://www.ico-op.eu.

- [2] K. Henke, St. Ostendorff, H.-D. Wuttke, Th. Vietzke, Ch. Lutze, "Fields of Applications for Hybrid Online Labs", International Journal of Online Engineering (iJOE), Vol 9 (2013) - Special Issue REV2013; pp. 20–30, Vienna, May 2013.

- [3] K. Henke, St. Ostendorff, St. Vogel, H.-D. Wuttke, "A Grid Concept for Reliable, Flexible and Robust Remote Engineering Laboratories", International Journal of Online Engineering (iJOE), Vol 8 (2012), pp. 42–49, Vienna, December 2012.

- [4] K. Henke, St. Ostendorff, H.-D. Wuttke, Th. Vietzke, Ch. Lutze, "Fields of Applications for Hybrid Online Labs", Remote Engineering & Virtual Instrumentation, REV2013, Sydney, Australia, 06–08 February 2013.

- [5] K. Henke, St. Ostendorff, H.-D. Wuttke, "A Flexible and Scalable Infrastructure for Remote Laboratories - Robustness in Remote Engineering Laboratories", The Impact of Virtual, Remote and Real Logistics Labs - ImViReLL2012 in: CCIS 282 pp. 13–24,

Springer Verlag, DOI: 10.1007/978-3-642-28816-6\_2, Bremen, Berlin, Heidelberg, February 2012. <u>http://dx.doi.org/10.1007/978-3-642-28816-6\_2</u>

- [6] K. Henke, St. Ostendorff, St. Vogel, H.-D. Wuttke, "A Grid Concept for Reliable, Flexible and Robust Remote Engineering Laboratories", International Conference on Remote Engineering and Virtual Instrumentation, REV2012, Bilbao, Spain, July 04–06, 2012.

- [7] Altera Corporation, <u>http://www.altera.com</u>.

- [8] Xilinx, Inc., http://www.xilinx.com.

- [9] MAX V CPLD, <u>http://www.altera.com/devices/cpld/max-v/mxv-index.jsp</u>

- [10] Quartus II Web Edition Software, <u>http://www.altera.com/products/</u> software/quartus-ii/subscription-edition/qts-se-index.html.

- [11] Quartus II Simulator Tools for Education, <u>http://www.altera.com/education/univ/software/qsim/unv-</u> qsim.html.

- [12] ModelSim-Altera Software, <u>http://www.altera.com/products/</u> software/quartus-ii/modelsim/qts-modelsim-index.html

- [13] http://www.ftdichip.com/Products/ICs/FT2232H.htm

- [14] sScience Website, http://www.esience.org

- [15] DesIRE Website, http://tempus-desire.thomasmore.be

### AUTHORS

**Karsten Henke** is with the Ilmenau University of Technology, Faculty of Computer Science and Automation, Integrated Communication Systems Group, 98684 Ilmenau, Germany, POB 10 05 65 (e-mail: karsten.henke@tu-ilmenau.de).

Galina Tabunshchyk is with the Zaporizhzhya National Technical University, Software Tools Department, 69063 Zaporizhzhya, Ukraine, Zhukovskogo 64, (e-mail: galina.tabunshchik@gmail.com).

**Heinz-Dietrich Wuttke** is with the Ilmenau University of Technology, Faculty of Computer Science and Automation, Integrated Communication Systems Group, 98684 Ilmenau, Germany, POB 10 05 65 (e-mail: dieter.wuttke@tu-ilmenau.de).

**Tobias Vietzke** is with the Ilmenau University of Technology, Master Student in Computer Engineering at the Faculty of Computer Science and Automation, 98684 Ilmenau, Germany, POB 10 05 65. He obtained his BSc. in Computer Engineering in 2011 (e-mail: tobias.vietzke@tu-ilmenau.de).

**Steffen Ostendorff** is with the Ilmenau University of Technology, Faculty of Computer Science and Automation, Integrated Communication Systems Group, 98684 Ilmenau, Germany, POB 10 05 65 (e-mail: steffen.ostendorff@tu-ilmenau.de).

This work was supported in part by the European Commission within the program "Tempus", "ICo-op – Industrial Cooperation and Creative Engineering Education based on Remote Engineering and Virtual Instrumentation", Grant No 530278-TEMPUS-1-2012-1-DE-TEMPUS-JPHES. Submitted 01 July 2014. Published as resubmitted by the authors 13 September 2014.