# A Virtual Laboratory for Digital Design

Domenico Ponta and Giuliano Donzellini

Department of Biophysical and Electronic Engineering, University of Genoa, Italy

Abstract—This paper presents a virtual laboratory for digital design, specifically conceived for educational application and for supporting project work both locally and at distance: the Deeds. It covers combinational and sequential logic networks, finite state machines, microcomputer interfacing and programming at assembly level. The virtual lab is based on three simulator integrated together, combined with a large repository of application projects, available on the web. The paper contains an example of a laboratory session, structured accordingly to the Project Based Learning methodology.

*Index Terms*—Circuit simulation, digital circuits, e-learning, virtual laboratory.

#### I. INTRODUCTION

The rapid development of digital electronic techniques that has taken place in the last two decades has had a profound impact on the design practices, demanding a new educational approach in the preparation of the professionals working in this field.

The complexity of today's systems and the wide variety of their different applications dictates the necessity of using sophisticated software for conception, design, testing and manufacturing. Currently, Computer Aided Design (CAD) techniques are an essential part of the system development process, while traditional design and prototyping techniques have lost part of their role. Professional software tools are generally available for educational institutions and more and more often used in education, sometimes even in introductory bachelor-level courses.

In our opinion, the use of a professional commercial simulator in a course designed to provide the foundations of digital design is not a good choice. A tool conceived to increase the productivity of a digital designer does not meet, albeit as its primary target, the needs of education. What is a plus for the professional (for instance the wide availability of components and functions) may be a minus for the learner. The now common use of Hardware Description Languages for design is an handicap when the learner lacks programming experience and the high level of abstraction may hide important basic phenomena.

In reality, the complexity of today's digital systems comes out of the variety and sophistication of the applications: per se, digital design is simple, provided that its founding elements are well understood and mastered. For instance, digital design is an almost ideal application field for Project (or Problem) Based Learning (PBL), since most of the training can take place during the development of projects, starting from a quite limited theoretical background.

The authors have explored in the past the use of interactive multimedia materials as learning tools to

facilitate understanding of the basic issues of digital design [1]. The pedagogical results suggested replacing most of them with a general purpose simulator. This is the rationale for the development of the Deeds (Digital Electronics Education and Design Suite), a virtual laboratory for educational application [2] [3].

#### II. THE DEEDS VIRTUAL LABORATORY

The Deeds has been developed by a group at DIBE (Department of Biophysical and Electronic Engineering, University of Genoa, Italy) as part of its research activities in the fields of project based, distance and cooperative learning. It is extensively used by the students of the first and second year of electronic and information engineering, to support laboratory activity and projectbases courses.

The virtual laboratory is based on three simulators: the Digital Circuit Simulator (d-DcS), the Finite State Machine Simulator (d-FsM) and the Microcomputer Emulator (d-McE). They cover, respectively, combinational and sequential logic networks, finite state machine design, microcomputer interfacing and programming at assembly level.

The simulators can work together, allowing therefore design and simulation of complex networks including a mix of standard logic, state machines and embedded microcomputers, as today's applications demand.

The virtual laboratory is integrated with a Main and an Assistant HTML browsers: the former enabling Internet navigation to find pages with information, exercises and laboratory assignments, the latter providing step-by-step guidance to students in their work.

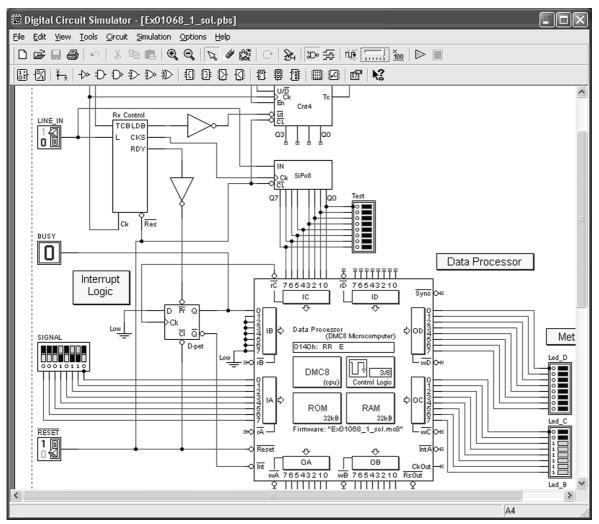

The d-DcS interfaces with the user through a graphical schematic editor (Fig. 1), providing a comprehensive library of logic components, implementing standard functions and not describing specific commercial products. The library includes also user-definable components that can defined as Finite State Machines (FSM) and built with the Finite State Machine Simulator. The 8-bit microcomputer component is accessible through standard input-output parallel ports, besides other inputs as clock, reset and interrupt request; the firmware of the board can be programmed at assembly language level.

To draw the schematic of a circuit the student picks up components from the toolbar, then connects them together using wires. Fig. 1 shows part of an embedded system based on Deeds' DMC8 microcomputer and including library standard components, and a FSM.

The user can test the whole network in two different modes. In the interactive mode, the student can "animate" the digital system in the editor, controlling its inputs and observing the results: such way of operation can be useful for the beginners. In the timing mode, as in professional simulators, the behaviour of the circuit is shown in a

A VIRTUAL LABORATORY FOR DIGITAL DESIGN

Figure 1. The schematic editor of the d-DcS.

timing diagram window, in which the user can define graphically an input signal sequence and observe the simulation results.

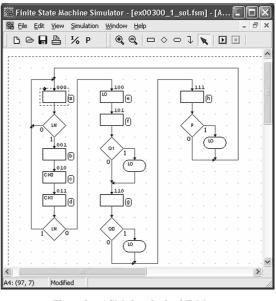

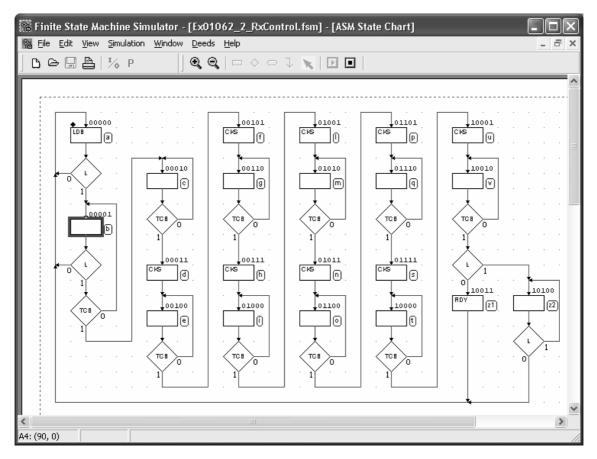

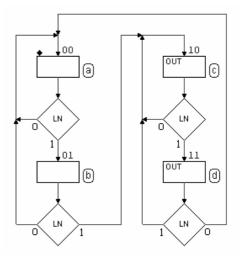

The d-FsM uses the ASM (Algorithmic State Machine) chart to graphically define the algorithm of finite state machines components (Fig. 2). The d-FsM functional simulation of the finite state machines provides the runtime display of state and timing evolution. FSM components can be directly used in the d-DcS and, also, exported as VHDL processes.

The d-McE is the tool for practicing embedded microcomputer programming and interfacing. The microcomputer component includes CPU, ROM and RAM memories, parallel I/O ports, reset circuitry and a simple interrupt logic. The custom 8-bit CPU (DMC8) is a simplified version of the 'Z80' processor. We have ruled out the possibility of emulating a state-of-the-art processor because its complex architecture would be an obstacle to understanding the basic principles of machine-level programming.

Figure 2. ASM chart in the d-FsM.

# A VIRTUAL LABORATORY FOR DIGITAL DESIGN

| ₩ Micro Computer Emulator - [Ex01068_1_sol.mc8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       | ×   |  |  |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----|--|--|--|--|--|--|--|--|

| File Edit Project Emulation Options View Help                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                       |     |  |  |  |  |  |  |  |  |

| Board Editor Debugger                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                       |     |  |  |  |  |  |  |  |  |

| V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V V                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |     |  |  |  |  |  |  |  |  |

| Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Memory                                                                                                | =   |  |  |  |  |  |  |  |  |

| Bit     7     0     Bit     7     0     IFF       A     0.00.00.00.00     00     F     0.00.00.00     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0     0 | Addr +0 +1 +2 +3 +4 +5 +6 +7 +8 +9 +A +B +C +D +E +                                                   |     |  |  |  |  |  |  |  |  |

| B 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0010 FF                                                           | 9   |  |  |  |  |  |  |  |  |

| D 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0020 FF                                                           |     |  |  |  |  |  |  |  |  |

| H 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0030 FF FF FF FF FF FF FF FF C3 5F 01 FF FF FF FF FF 1<br>0040 FF |     |  |  |  |  |  |  |  |  |

| Bit 15 \$ 7 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 0040 FF                                                           |     |  |  |  |  |  |  |  |  |

| X 000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0060 FF                                                           |     |  |  |  |  |  |  |  |  |

| IX 000000000000000000000000000000000000                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 0070 FF                                                           | -   |  |  |  |  |  |  |  |  |

| SP 00000000000000 FFFD PC 0154 V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                       |     |  |  |  |  |  |  |  |  |

| I / 0 Ports                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Object Code                                                                                           | _   |  |  |  |  |  |  |  |  |

| IN Bit 7 0 Bit 7 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Addr Op Code Label Istruction Comme:                                                                  |     |  |  |  |  |  |  |  |  |

| [00] IA 00000000 00 [02] IC 00000000 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 014E 7B LD A,E                                                                                        | -   |  |  |  |  |  |  |  |  |

| [01] IB 0 0 0 0 0 0 0 [03] ID 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 014F D303 OUT (LED_D),A                                                                               |     |  |  |  |  |  |  |  |  |

| 1901 1B 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 0151 C30F01 JP MAINLOOP                                                                               |     |  |  |  |  |  |  |  |  |

| OUT Bit 7 0 Bit 7 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0154 3E00 CLRLEDS LD A,0 ;                                                                            |     |  |  |  |  |  |  |  |  |

| [00] OA 00000000 00 [02] OC 000000000 00                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 0156 D300 OUT (LED_A),A ;Clea                                                                         |     |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 0158 D301 OUT (LED_B),A                                                                               | all |  |  |  |  |  |  |  |  |

| [01] OB 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 015A D302 OUT (LED_C),A                                                                               | 9   |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 015C D303 OUT (LED_D),A                                                                               |     |  |  |  |  |  |  |  |  |

| Info                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | O15E C9 RET                                                                                           |     |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 015F F5 INTERRUPT PUSH AF ;Save                                                                       | 1   |  |  |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                       |     |  |  |  |  |  |  |  |  |

| CAPS INS NUM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                       |     |  |  |  |  |  |  |  |  |

Figure 3. The interactive debugger of d-McE.

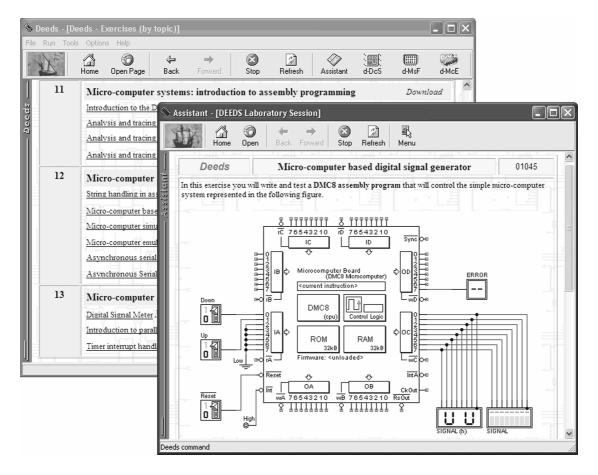

Figure 4. A virtual laboratory project assignment.

The d-McE source code editor enables user to enter programs, and a simple command assembles, links and loads them in the emulated system memory. Programs can be executed step by step in the interactive debugger (Fig. 3), where the user can observe, at the same time, the contents present in all the structures involved in the hardware/software system. In Fig. 3, the CPU register bank is placed on the top left and the Input/Output ports on the bottom left. On the right are visualized: the ROM and RAM memory contents (top) and the object and assembly code of the loaded program (bottom). The instruction under execution is highlighted, as well as a breakpoint set by the user.

# III. PEDAGOGICAL ASPECTS OF THE VIRTUAL LABORATORY

In our environment, traditional lectures coexist with a problem-based laboratory, accessed either from a PC classroom, with tutorial assistance, or in distant mode. In both cases, virtual laboratory sessions are delivered as resources of Moodle Learning Management System (LMS) [4].

A typical virtual laboratory assignment is a project, presented as an HTML document with text and figures. Fig. 4 shows a project assignment (foreground), chosen from the Deeds website repository (background). In this specific case the user is requested to design a digital signal generator by programming a given microcomputer hardware.

Text, figures and visual objects can be linked to the editing and simulation tools of Deeds. For example, let's suppose to assign a problem in the form of a schematic to analyse/modify. When the user clicks on the schematic, Deeds launches the corresponding simulator, and opens that schematic in it. As necessary, the Deeds open another browser (the Assistant) that can contain more information on how to design, explore or test the circuit itself. Such procedure is equally useful to convey concepts both on simple components and on more complex networks.

Project development phases may be guided by help and instructions supplied through the Assistant browser. This is mostly the case with introductory projects, where a stepby-step guidance may be in order. In more advanced projects the use of the simulation tools is less guided and left more to the user initiative.

An important features of Deeds is the ability to deliver a suitable trace of the solution (i.e. a partial schematic of the solution), or a set of stimulus signals, ready to be used to check the behaviour of the digital circuit under test. Using this approach, students can be guided to the desired level of problem solving, for example avoiding repetitive tasks. A proper template for the project deliverables speeds up the preparation of the lab report, allowing the student to concentrate more in the project work.

## IV. EXAMPLE OF A VIRTUAL LAB SESSION

Deeds lends itself very well as a tool for PBL. Learners download from the LMS the project assignment, generally a functional description and a set of specifications of a system they must design. We do not provide detailed instruction and explanations: instead, the project to develop is only an element of a set related projects, of different difficulty, joined together by the fact that they explore different facets of a main issue.

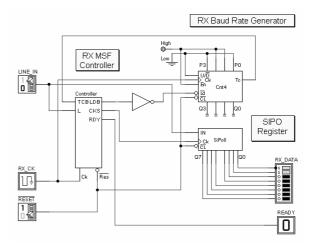

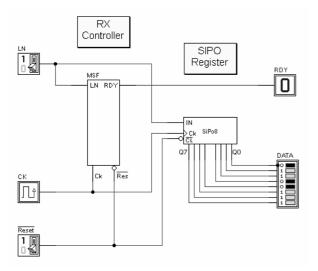

Figure 5. Asynchronous serial receiver architecture.

The learner can move freely within them and choose if attacking directly the main one or reinforce his knowledge by approaching first the simpler ones.

Serial data communication is a subject that allows to explore several aspects of digital design. As an example, therefore, we present here a set of projects having for final target the design of an 8-bit asynchronous serial receiver.

Since this problem could be approached in different ways and the student does not possess yet the capabilities to develop it from scratch, we propose as a common starting point the system architecture, of which the control unit must be designed (Fig. 5). The set of specifications to satisfy, such as the format of the serial data, is submitted to the student.

Using Deeds, the controller can be designed as FSM. A possible solution to the problem is shown in Fig. 6, as an ASM chart, composed of 21 state blocks (the rectangles) and a certain number of decisional blocks.

The learners test the controller's design with the Finite State Machine Simulator. Next, they connect the controller to the given architecture and simulate the whole system with the Digital Circuit Simulator. Fig. 7 shows a typical result in the form of timing diagram.

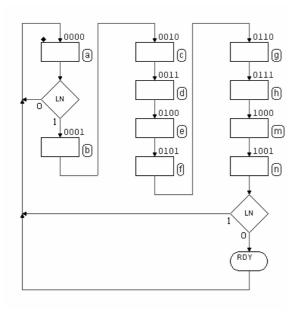

Usually, students wish to familiarize themselves with simpler problems, before solving the final one. The problem of Fig. 8 asks for the design of a synchronous serial receiver, whose architecture has been simplified by removing the sampling clock generator. The serial signal protocol is the same, but the system now uses a sampling clock coming from outside. As in the previous case, the students' task is the design of the control algorithm. It must be noted, though, that the problem is not a subset of the previous one, but has different specifications, to avoid repetitions and keep attention alive. Fig. 9 presents a possible FSM controller (the solutions to the problem are presented here to provide first-hand information on the level of difficulties).

In the pedagogical practice of PBL we do not publish any solution, expecting that students test by themselves the functionality of their design with Deeds's simulators. A correct design is the one that operates accordingly to the specifications. This target is achieved by successive design and testing phases. Pedagogically speaking, we are trying to remove the concept of "solution" when talking about digital projects. Not a solution but a design, in

## A VIRTUAL LABORATORY FOR DIGITAL DESIGN

Figure 6. ASM chart of the synchronous serial receiver controller.

| 🕮 d-DcS - Timing                          | Diagra  | m - (Timing Int | terval Sim       | ulation mode | )        |              |          |                | - DX          |  |  |

|-------------------------------------------|---------|-----------------|------------------|--------------|----------|--------------|----------|----------------|---------------|--|--|

| ◎ 5 9 9 9 9 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 |         |                 |                  |              |          |              |          |                |               |  |  |

| RESET                                     |         |                 |                  | 1mS          | <u> </u> |              | 2 m      | nS             |               |  |  |

| Ш RX_CK                                   | ) Minim |                 | LĖĻININININI     |              |          |              |          |                |               |  |  |

| 문 LINE_IN                                 |         |                 | <u></u>          |              |          |              |          |                |               |  |  |

| 🔠 RX_DATA                                 | (00h    |                 |                  | <b>∦</b> 80h | (COh     | <b>≬</b> 60h | (30h     | (198h          | (CCh          |  |  |

| READY                                     |         |                 |                  |              |          |              |          |                |               |  |  |

| 📰 👄 Controller                            |         | <b>X</b> 00010  | <u>)</u> ()00100 | ₩00110       | XX 01000 | XX01010      | XX 01100 | 01110          | <u>∦10000</u> |  |  |

| - State                                   | a (b    | ) c             | Щe               | Щg           | Xi 🗌     | <u>))(</u> m | Щ°       | Щ q            | <u>X</u> t    |  |  |

| - TCB                                     |         | <u> </u>        | <u>n</u>         |              |          |              |          |                |               |  |  |

| -LDB                                      | lL      |                 |                  |              |          |              |          |                |               |  |  |

| L_CKS                                     |         |                 | Π                | Π            |          |              |          | П              | <u> </u>      |  |  |

|                                           |         |                 |                  |              |          |              |          |                |               |  |  |

|                                           |         |                 |                  |              |          | 643,072      | .s       |                |               |  |  |

|                                           | 44 4 4  | H > + + = 4     |                  |              |          |              |          |                | <u> </u>      |  |  |

|                                           |         |                 |                  |              |          |              |          | 4,096 µS/pixel | //            |  |  |

Figure 7. d-DcS timing simulation of the asynchronous serial receiver.

almost all cases not a unique one. The role of the simulator is therefore central to our PBL methodology, since it makes the learner autonomous in its work, removing the need to have somebody checking the projects.

The approach of providing a set of exercises of decreasing difficulty is quite flexible, since any problem may make a reference to a simpler one. It is possible, therefore, to build a complete course on the basis of PBL paradigm.

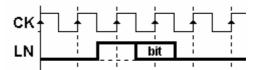

As an example, the following entry-level problem "one bit" serial receiver, (Fig. 10) reduces the process of serial data acquisition to its simplest aspect, allowing the learner to concentrate on the principle. In this case, the system does not need external components, by using directly inputs and outputs of the control unit. The design is represented by the FSM algorithm, shown in Fig. 11.

Figure 8. A simple synchronous serial receiver.

Figure 9. Synchronous serial receiver controller.

#### V. CONCLUSIONS

In a course supported by the virtual laboratory, acquisition of knowledge and skills takes place through the development of problems graduated by subject and difficulty. A large repository of problems is already available [2].

Using the virtual laboratory, students can check by themselves their results and correct their mistakes, assuring, therefore, the self-consistence of their work, as it is the case of the professional designers.

The integration of the virtual laboratory with a Learning Management System provides added value for teachers and students alike. Teachers can keep track of students' activity, provide news and guidance, and have access to the project deliverables. Students may carry on the project locally or remotely, can exchange information with their peers and get help by the teachers through the discussion forums.

Figure 10. The very simple timing serial sequence of the "one bit" serial receiver.

Figure 11. . Simple "one bit" serial receiver

At the level of instruction exemplified in this paper, the virtual laboratory may support or replace traditional hardware laboratories, providing several advantages, such as savings of time and resources, de-localisation, better integration with courses. The loss of physical contact with components, circuits and instruments is in line with the evolution of design techniques, which has made obsolete most of the traditional hardware experimentation and prototyping, replacing them with simulation [5, 6, 7, 8].

Deeds has been extensively and successfully used in our institution by thousands of students of the first and second year of the information engineering curricula, as a support to traditional teaching, effectively replacing traditional hardware laboratories. A thorough discussion of the tradeoffs between real and virtual laboratories in electronics is contained in [7].

Deeds has been specifically designed to support Project Based Learning not only in a local context but also in a geographically de-localized environment. Therefore it lends itself very well both for local and distance education and has the capabilities to extend project work within an inter-institutional and international context, as demonstrated by the results of NetPro (Network Based Project Learning) [9], a European project of the Leonardo DaVinci programme. Several colleagues from European universities have adopted Deeds in their teaching.

#### REFERENCES

- G. Da Bormida, D. Ponta and G. Donzellini, "Methodologies and Tools for Learning Digital Electronics," *IEEE Trans. on Education*, Vol. 40, No. 4, abstract p. 294, full paper on CD, 1997.

- [2] Deeds website: http://www.esng.dibe.unige.it/netpro/Deeds/

- [3] G. Donzellini and D. Ponta, "A Simulation Environment for e-Learning in Digital Design," *IEEE Trans. on Industrial Electronics*, vol. 54, no. 6: 3078-3085, December 2007.

- [4] Moodle website: <u>www.moodle.org</u>

- [5] L. S. Indrusiak, M. Glesner and R. Reis, "On the Evolution of Remote Laboratories for Prototyping Digital Electronic Systems," *IEEE Trans. on Industrial Electronics*, vol. 54, no. 6: 3069-3077, December 2007.

- [6] L. Gomes, "Programmable logic devices supporting embedded system design curriculum," in Proc. 31st Annual Conference of IEEE, IECON 2005, Industrial Electronics Society, paper on CD, 6-10 Nov. 2005.

- [7] G. Donzellini and D. Ponta, "The electronic laboratory: traditional, simulated or remote?," Advances on re-mote laboratories and elearning experiences, L. Gomes and J. Garcia-Zubia, Ed. Bilbao: University of Deusto, pp. 223–246, 2007.

- [8] Jing Ma and J. V. Nickerson, "Hands-on, simulated, and remote laboratories: A comparative literature review," ACM Computing Surveys, Vol. 38, No. 3, Article No. 7, pp 1-24, Sep. 2006.

- [9] D. Ponta, G. Donzellini and H. Markkanen, "Electronic system design: an experiment of project-based learning on network," *European Journal of Engineering Education*, Vol. 26, No. 4, pp. 375-390, 2001.

## AUTHORS

**D.** Ponta is with the Department of Biophysical and Electronic Engineering, University of Genoa, Genoa, Italy (e-mail: ponta@unige.it).

**G. Donzellini** is with the Department of Biophysical and Electronic Engineering, University of Genoa, Genoa, Italy (e-mail: donzie@unige.it).

Manuscript received 27 March  $\,$  2008. Published as submitted by the authors.